Digital I/O Wildcard Users Guide

This document describes how to use the Digital I/O WildcardTM, providing an overview of the hardware and software and a schematic. The Digital I/O Wildcard allows you to easily add up to 20 lines of digital I/O (input/output) to your instrumentation application. It can be used to expand the I/O of any of Mosaic’s controller products. The following sections guide you through the Digital I/O Wildcard’s hardware and software.

Hardware

The Digital I/O Wildcard expands the digital IO capabilities of Mosaic embedded instrument controllers. This 2" x 2.5" card provides 16 channels configurable in groups of four as either inputs or outputs plus 4 additional digital input channels. Each line is configurable for pull up, pull down, or tri-state operation. Outputs sink up to 24 mA or source up to 4 mA continuously.

The following sections show you how to hook up the Digital I/O Wildcard to your controller, how to select the Wildcard address, and how to configure each I-O line for pull-up, pull-down, or tri-state operation.

Specifications

| Digital I/O Wildcard Specifications | |

|---|---|

| Channels: | Configurable Channels: 16, configurable as input or output in groups of 4 Fixed Input Channels: 4 |

| Inputs: | Input Voltage Range: 0 – 5 V ( -0.5 to 5.5 absolute max) Input Low Voltage: < 0.80 V Input High Voltage: > 2.0 V Input Leakage Current: ± 10 μA Input Capacitance: 10 pF |

| Outputs: | Output Voltage Range: 0 – 5 V ( -0.5 to 5.5 absolute max) Output Low Voltage: < 0.5 V at 24 mA (i.e., 12Ω typ., 21Ω worst case) Output High Voltage: >3.5 V typ., 5.0 V pulled up, >2.4 V at -4.0 mA Output Current: 24 mA sink, 4 mA source Max Output Current: 100 mA on any pin Max Internal Power: 250 mW all pins together |

| Pull up/down: | Optional Pull-up/down : 10 KΩ, jumper selectable pull up/down |

| Current: | 60 mA from 5V on Wildcard bus, plus I/O current |

| Weight: | 23 gram |

| Size : | 2" x 2.5" x 0.365"1) (50.8mm x 63.5mm x 9.3mm) |

Connecting to the Mosaic controller

To connect the Digital I/O Wildcard to a Wildcard-ready Mosaic controller or to a Wildcard Carrier Board, follow these simple steps:

With the power off, connect the Wildcard Bus on the Digital I/O Wildcard to Wildcard Port 0 or Wildcard Port 1 on your controller or the Wildcard Carrier Board (These may also be called Module Port 0 or 1). If you are using a Wildcard Carrier Board, connect it to the QED Board as outlined in the "Wildcard Carrier Board Users Guide". The corner mounting holes on the Wildcard should line up with the standoffs on your controller.

Selecting the Wildcard address

Once you have connected the Wildcard you must set the address of the module using jumper shunts across J20 and J21. These Wildcard Select Jumpers select a 2-bit code that sets a unique address on the Wildcard port of the Mosaic controller. Each Wildcard port on the controller board accommodates up to 4 Wildcards. Wildcard Port 0 on the Mosaic controller provides access to Wildcards addressed at locations 0-3 while Wildcard Port 1 provides access to Wildcards 4-7. Two Wildcards on the same port cannot have the same address (jumper settings). Use the following table to select jumper settings and the corresponding addresses.

| Address Jumper Settings | ||

|---|---|---|

| Wildcard Port | Wildcard Address | Installed Jumper Shunts |

| 0 | 0 | None |

| 0 | 1 | J1 |

| 0 | 2 | J2 |

| 0 | 3 | J1 and J2 |

| 1 | 4 | None |

| 1 | 5 | J1 |

| 1 | 6 | J2 |

| 1 | 7 | J1 and J2 |

| Note:<block indent>Address 0 is not available on the QScreen or Handheld. Use addresses 1 through 7 instead.</block> | ||

Configuring the digital I/O lines

You may configure each I/O line for pull-up, pull-down, or tri-state operation. This allows you to set the appropriate level of each I/O line between power-up and software initialization.

There are twenty three-post jumpers on the Digital I/O Wildcard labeled J0-J19. The labels are located next to each jumper post. The jumpers are used to configure the twenty digital I/O lines for pull-up, pull-down, or tri-state operation. To configure a digital line for pull-up operation, simply install a jumper shunt across the two jumper posts above the + sign located next to the jumper label. To configure a digital line for pull-down operation, install the jumper shunt across the two pins above the – sign. By not installing a jumper shunt, the line is configured for tri-state operation.

Once you have connected and configured all of the hardware, you can use the software drivers to read or set the digital lines.

Current capability of the digital output lines

The inputs and outputs are all provided by a single device, a Xilinx CPLD, XC9536.

The digital outputs provide TTL-compatible levels for driving logic devices. But you can also control devices, such as relays and light emitting diodes, that require more current. You can either provide current from a digital output high, or you can sink current into a digital output low. Generally speaking, the output low is capable of sinking much more current than the output high can source, and using it results in lower power dissipation. So if you need substantial current, you should turn on the external device by sinking current from it using an output low.

As an output is loaded, its voltage level, VOL or VOH, rises or falls with the current. It is often useful to know just how much to expect the VOL and VOH levels to degrade with current. For currents of less than 100 mA the voltage change is approximately linear with current; that is, it can be modeled as a voltage source of either zero volts (for an output low) or 3.3 volts (for an output high) and an equivalent series resistance. At greater output currents the resistance becomes nonlinear, but you shouldn’t ever source or sink more than 100 mA, and you should not source or sink more than 25 mA continuously.

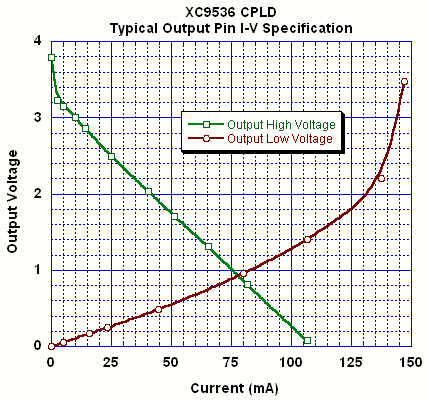

The Wildcard uses a Xilinx CPLD (XC9536) to provide the digital outputs. The following figure shows the degradation of output voltage high and low levels with increasing source or sink current for a typical device.

An output high is typically 3.8 V, but rises to 5 V when the pull-up jumper is installed. As current is drawn by an external device the voltage drops, appearing as a 3.3 volt source and a 30 Ω resistance. That is,

VOH = 3.3 V – 30 Ω * Isource

The output impedance for an output low is considerably less, allowing it to sink more current than an output high can source. With no current, the output low is zero volts, and it increases with current as a 12 Ω resistance (12 Ω typically, 21 Ω worst case), up to a limit of approximately 100 mA:

VOL = 12 Ω * Isink

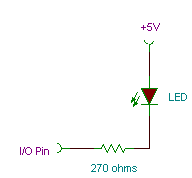

The above graph and equations can be used to choose component values for particular circuits. For example if we wish to use an output low to drive a light-emitting diode we would place the LED in series with a resistor and connect them between an output pin and a +5V supply, like this,

The resistor limits the current through the LED and into the output low. From the LED data sheet we note that its forward voltage at a current of 10 mA is specified to be 2.2 V. What should the resistor value be? We calculate it as,

R = (5V-2.2V - VOL) / 10 mA

Consulting the VOL vs I curve for the output pin we find that at 10 mA VOL = 0.12V. We therefore need a resistance near 270 ohms.

Protecting the input and output pins

These output pins are very useful because they can directly drive a wide range of devices. Nevertheless, any circuitry connected to them should take care to:

- Prevent excessive voltage levels at the pin;

- Prevent excessive currents; and,

- Prevent excessive power in the Wildcard.

We’ll address each of these concerns in turn.

Preventing Excessive Voltages: Excessive voltages are prevented by ensuring that voltages of less than a diode drop below ground (-0.5 V) or greater than a diode drop above 5V (5.5 V ) are never applied to an output pin. For some applications, particularly when driving inductive loads such as relays, you may need to provide Schottkey diode clamps between the pin and +5V and between the pin and ground. If an output pin is directly connected to a voltage source below ground or above 5V the Wildcard will be destroyed. Whenever possible, it’s a good idea to drive external devices through a current limiting resistor (say 100 Ω).

Preventing Excessive Currents: The current into or out of any output pin on the Wildcard should also be limited to prevent damage. These pins can withstand brief source or sink currents of up to 100 mA at room temperature, but you should never allow currents greater than 100 mA. Load circuitry that requires significant current to be sourced or sunk by the digital output should include external resistors to ensure that an absolute maximum rating of 100 mA on a single output pin is never exceeded.

Preventing Excessive Power: Never cause more than 250 mW of I/O pin power to be dissipated on the Wildcard. The total power allowed is the sum of the power dissipated by each pin. For output highs that power is the product of the source current and the difference between +5V and VOH. For output lows that power is the product of the sinked current and VOL. A limitation of the total power to 250 mW is actually quite generous. Note that from the above figure, when 25 mA is sunk into an output low the power contributed is only 7.5 mW (for a typical device, max of 12.5 mW for any device). Consequently, you can continuously sink 25 mA into all the output pins simultaneously.

Connecting to the field header

All connections to the Wildcard should be made throught the Field Header, H2. This right-angle header provides the 20 I/O lines as well as power and ground connections.

Table 1-3: Digital I/O Field Header H2

| Signal | Pins | Signal | |

|---|---|---|---|

| GND | – 1 | 2 – | +5V |

| GND | – 3 | 4 – | V+RAW (5.5-26V) |

| Input 19 | – 5 | 6 – | Input 18 |

| Input 17 | – 7 | 8 – | Input 16 |

Input/Output 15 | – 9 | 10 – | Input/Output 14 |

| Input/Output 13 | – 11 | 12 – | Input/Output 12 |

| Input/Output 11 | – 13 | 14 – | Input/Output 10 |

| Input/Output 9 | – 15 | 16 – | Input/Output 8 |

| Input/Output 7 | – 17 | 18 – | Input/Output 6 |

| Input/Output 5 | – 19 | 20 – | Input/Output 4 |

| Input/Output 3 | – 21 | 22 – | Input/Output 2 |

| Input/Output 1 | – 23 | 24 – | Input/Output 0 |

Software

This section describes the software that enables you to control the Digital I/O Wildcard. Briefly, the Wildcard is accessed by functions that take the Wildcard’s physical address, and the offset of each nibble. The direction (as inputs or outputs ) of each nibble of the I/O is configured by calling IOSetBits or by calling Init_IO_Direction which is a function provided in the demo program. Inputs are read by calling IOFetchChar and outputs are written by using the same parameters with IOStoreChar.

Setting the direction of the I/O lines

The functions IOStoreChar, IOFetchChar, IOSetBits, and IOClearBits are used are used to communicate with the Digital I/O Wildcard. These functions take an offset address and Wildcard address. These functions are provided in "QED_QCard_IO.4th" for V4.xx kernels, but are native to the V6.xx kernel. This file can be found in:

Mosaic\Wildcard Drivers\Libraries\include\

The 20 digital I/O lines on the Digital I/O Wildcard are organized into five 4-channel groups or nibbles. The five nibbles are accessed using offset addresses 00H to 04H. The four digital I/O lines (digital inputs 15-19) at 04H are read-only inputs. I/O lines 0-15 are configured using a direction offset at 05H. Each bit of the least significant 4-bit nibble of the direction register controls the direction of four digital I/O lines. Table 2 summarizes the organization of the digital I/O lines.

Table 2: Organization of the Digital I/O Lines

| Offset | Name | Digital Lines | Direction |

|---|---|---|---|

| 00 | Nibble 0 | 0 – 3 | Inputs/Outputs |

| 01 | Nibble 1 | 4 – 7 | Inputs/Outputs |

| 02 | Nibble 2 | 8 – 11 | Inputs/Outputs |

| 03 | Nibble 3 | 12 – 15 | Inputs/Outputs |

| 04 | Nibble 4 | 16 – 19 | Inputs |

| 05 | Direction Register | – – | – – |

In setting the direction, a one in a bit position in offset 05H causes the corresponding nibble of I/O to be an output and a zero sets it as an input. The least significant bit of offset 05H controls the direction of the lowest four output lines (those whose values are controlled by offset 00H), the next bit of offset 05H controls lines 4-7 (whose values are set by offset 01H) and so on. The upper nibbles of offset 00H through 05H do nothing.

For example, for a Wildcard addressed at location 3, from the Forth terminal you could set the direction of digital lines 0 through 7 to outputs and 8 through 15 as inputs by executing,

HEX 03 05 03 IO.C! \ Sets bits 0 and 1 to one \ and bits 2 and 3 to zero at offset 05 for wildcard 03

Setting bits 0 and 1 to one configures the lower two nibbles, that is, lines 0 through 7, as outputs. And setting bits 2 and 3 to zero configures the next two nibbles, lines 8 through 15, as inputs.

The output lines would immediately assume the values provided by the contents of offsets 00 through 01 (so you might want to initialize them first!). You could send alternate output highs and lows to lines 0 through 7 by executing,

0A 00 03 IO.C! 0A 01 03 IO.C!

At each of the nibble locations there are separate read and write registers – you can read only from the read register and you can write only to the write register. For example, whatever the value you read from offset 00H, the values writtten to lines 0 through 3 when the direction is set to output will be the last nibble written to 00H. Also, whether the pins are configured as inputs or outputs, reading from 00H will always return the actual pin values, and not necessarily what you last wrote to 00H.

On power up, all of the digital I/O lines are initialized as inputs. Initializing the direction of the digital I/O lines is similar to setting the direction of Port A or Port C. The following C and FORTH code presents an example routine to set the direction of the I/O lines on the Digital I/O Wildcard.

C demonstration program

The C demo is located in your installation directory. It is also provided here for your reference.

Forth demonstration program

The Forth demo is located in your installation directory. It is also provided here for reference. After sending the demo to your board type:

Run_Demo

to start the demo.

Conclusion

Now you are ready to start using your Digital I/O Wildcard. All of the software routines listed in this document are also included with the development environment provided with your Mosaic controller starter kit.