Wildcard Bus Loading Limits

Introduction

Communication between Mosaic's Single Board Computers and our Wildcard™ Modular I/O Boards is implemented with a parallel bus known as the Wildcard Bus or Module Bus. The 24 lines on this bus include eight multiplexed address/data signals, three module select signals (allowing a maximum of 8 addressable Wildcards), power and ground, reset, and several additional control and clocking signals. On all controllers and most Wildcards, the Xilinx XC9536 or XC9536XL CPLD (Complex Programmable Logic Device) coordinates the communication over the Wildcard Bus; for more information, see the Digital I/O Wildcard Users Guide. On some Wildcards, other chips also directly connect to the data signals on the Wildcard Bus.

While the inputs of the CPLD and other chips draw very little steady-state current from the bus signals, each input has a small amount of capacitance, on the order of five to ten picofarads, that must be charged to a new voltage whenever a bus signal changes state. This limits the rate at which bus signals can transition from one state to another — the higher the capacitance, the slower the state change. The capacitance of all chips connected to the bus adds together, and if the sum of capacitance causes transitions exceed the bus timing allowances, data corruption will occur. The sum of capacitance on the bus is referred to as "capacitive load".

In addition, there is a small amount of inductance inherent in any flow of electric current, regardless of whether it is flowing through a device intended to be an inductor. If there is a maximum stack of four active Wildcards, perhaps plus additional passive Wildcards (those lacking a CPLD or other components connected to the Wildcard bus), the length of the signal path through the stacked Wildcard bus connector can represent an inductance sufficient to cause signal degradation. See below for specific methods to mitigate inductive interference.

Capacitive Load Limits

A controller board hosting a stack of eight Wildcards with only a single bus-connected CPLD on each results in a capacitive load on the Wildcard Bus that is well within the limits of the bus timing. However, when a stack contains multiple Wildcards with high capacitive loading (due to other bus-connected chips), it is possible for bus timing to degrade to the point that data corruption occurs.

We have simplified the calculation of capacitive loading on the Wildcard Bus by assigning a "load factor" to each Wildcard, and a "load factor limit" to each controller (e.g., QCard Controller or PDQ Board). The load factor for each Wildcard depends on the number of components on it that connect to the data signals of the Wildcard Bus. The load limit for a controller is dependent on the size of its circuit board and resulting length of copper traces implementing the Wildcard Bus.

When considering a combination of Wildcards to use with a particular controller, add up the load factors for those Wildcards, and ensure that the result is no more than the load factor limit for your controller. Please note that this simplified loading analysis technique is an inexact method of accounting for capacitive loading, so when operating at or near the load limit, testing of the controller/Wildcard stack is necessary to ensure reliability over the operating temperature range.

Controller Load Limits

| Controller | Wildcard Bus Capacitive Load Factor Limit |

|---|---|

| PDQ Board or QED Board with a Wildcard Carrier Board | 18 |

| QCard Controller | 16 |

| Graphical Controllers: QScreen Controller, Handheld (Legacy), QVGA (Legacy) | 14 |

Wildcard Load Factors

| Wildcard | Wildcard Bus Capacitive Load Factor |

|---|---|

| Thermocouple Wildcard | 6 |

| Analog I/O Wildcard | 4 |

| Keypad/Display Wildcard | 4 |

| Compact Flash Wildcard | 2 |

| UART Wildcard | 2 |

| AC Relay Wildcard | 1 |

| DA 24/7 Wildcard | 1 |

| DC Relay Wildcard | 1 |

| Digital I/O Wildcard | 1 |

| Ethersmart Wildcard | 1 |

| GPS Wildcard | 1 |

| Motor Control Wildcard | 1 |

| Power I/O Wildcard | 1 |

| USB Wildcard | 1 |

| WiFi Wildcard | 1 |

| Conductivity Sensing Wildcard | 0 |

| I/O Filter Wildcard | 0 |

| LCVR Driver | 0 |

| Prototyping Wildcard | 0 |

| PWM Driver Wildcard | 0 |

| Screw Terminal Wildcard | 0 |

| Signal Conditioning Wildcard | 0 |

Reducing Wildcard Bus Inductance

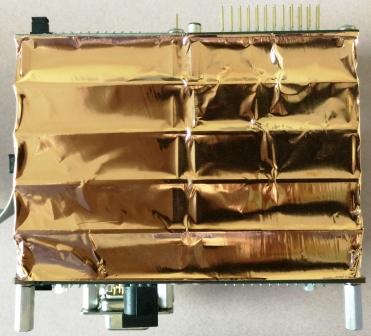

The most straightforward method for reducing inductance is to add shielding to the back of the Wildcard stack, allowing a return path for inductive effects. This can be accomplished with shielding tape made of copper or aluminum, which may have the effect of reducing electromagnetic interference (EMI) as well. If conductive tape is used for shielding, it is imperative to assure that the tape does not contact any signals other than frame ground (the aluminum standoffs).

Shielding Wildcard Bus with Copper Tape

As a more drastic measure, depending on the combination of Wildcards you are using it may be possible to arrange them such that some signals may be removed from the Wildcard bus at locations above which no Wildcards are using them. This means cutting some pins of the stacking Wildcard bus connectors once your arrangement of Wildcards is finalized if the above Wildcards do not use the signals carried by those pins. Contact Us for advice on whether this may be helpful and design assistance on your arrangement of Wildcards.

Examples

Here are two examples of calculating the total capacitive load factor for Wildcard combinations that are at the limit of a controller they might be used with.

| QScreen: Load Factor Limit = 14 | |||

|---|---|---|---|

| Wildcard | Load Factor | Qty | Total Load |

| Thermocouple Wildcard | 6 | x1 | 6 |

| Analog I/O Wildcard | 4 | x1 | 4 |

| UART Wildcard | 2 | x2 | 4 |

| Total: | 14 | ||

| PDQ Board: Load Factor Limit = 18 | |||

|---|---|---|---|

| Wildcard | Load Factor | Qty | Total Load |

| Thermocouple Wildcard | 6 | x1 | 6 |

| Analog I/O Wildcard | 4 | x2 | 8 |

| Keypad/Display Wildcard | 4 | x1 | 4 |

| Total: | 18 | ||